时序逻辑模块

- 锁存器

- 性质

- 锁存器是透明的,输入改变后输出就会改变。

- 常用模块

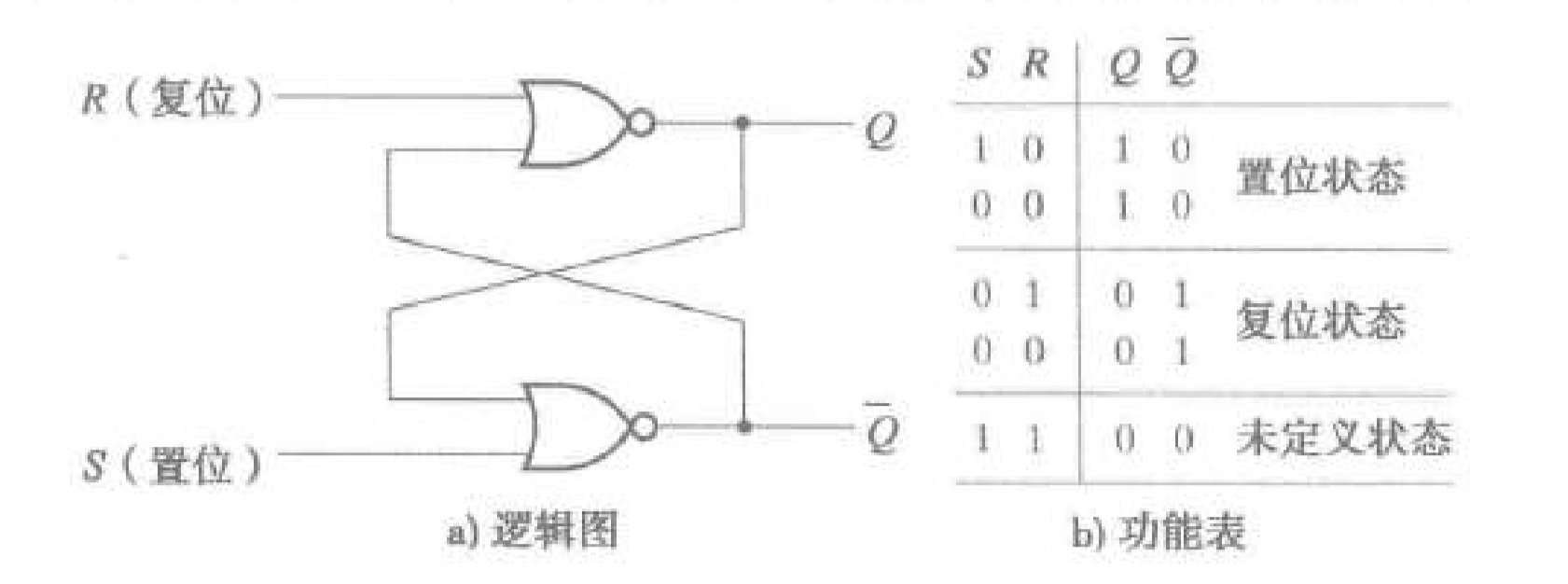

- 锁存器

- 锁存器是使用或非门的锁存器。

- 是锁存器保持状态, 时改状态为 , 时改状态为 。

- 是非法状态。

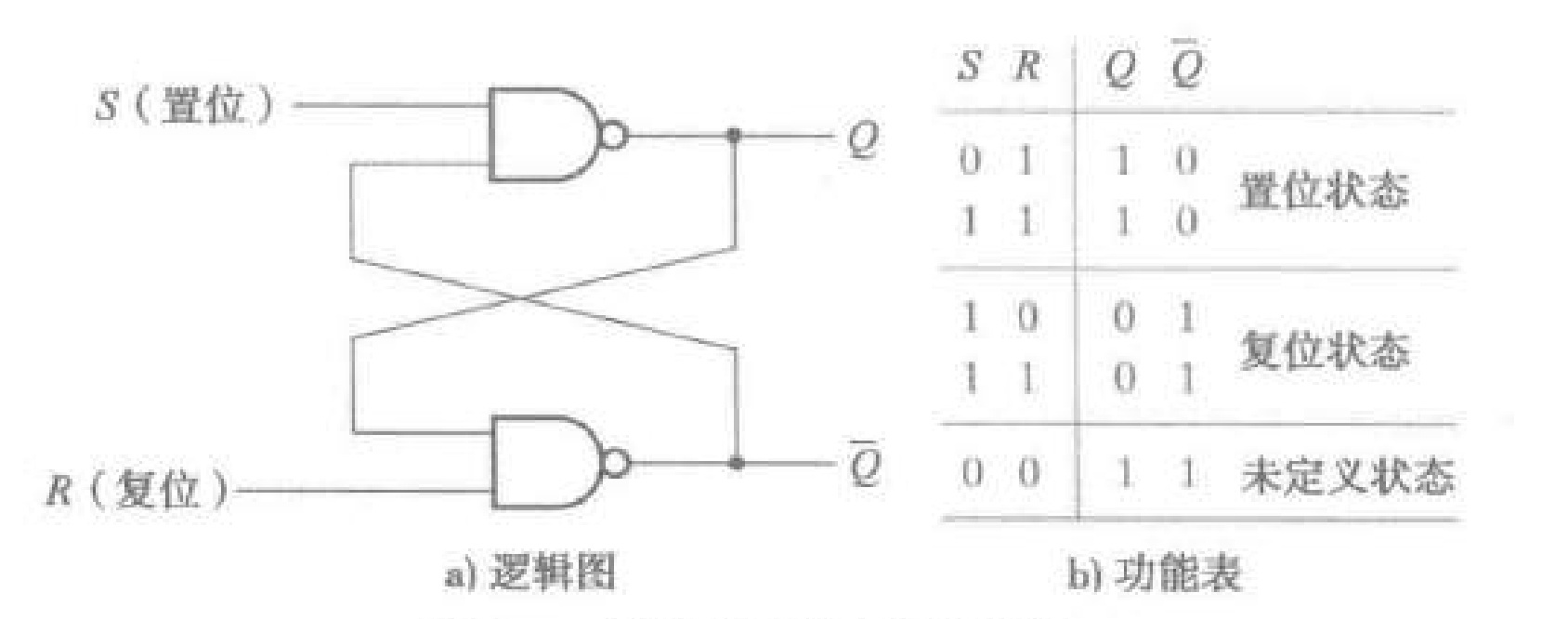

- 锁存器

- 锁存器是使用与非门的锁存器。

- 是锁存器保持状态, 时改状态为 , 时改状态为 。

- 是非法状态。

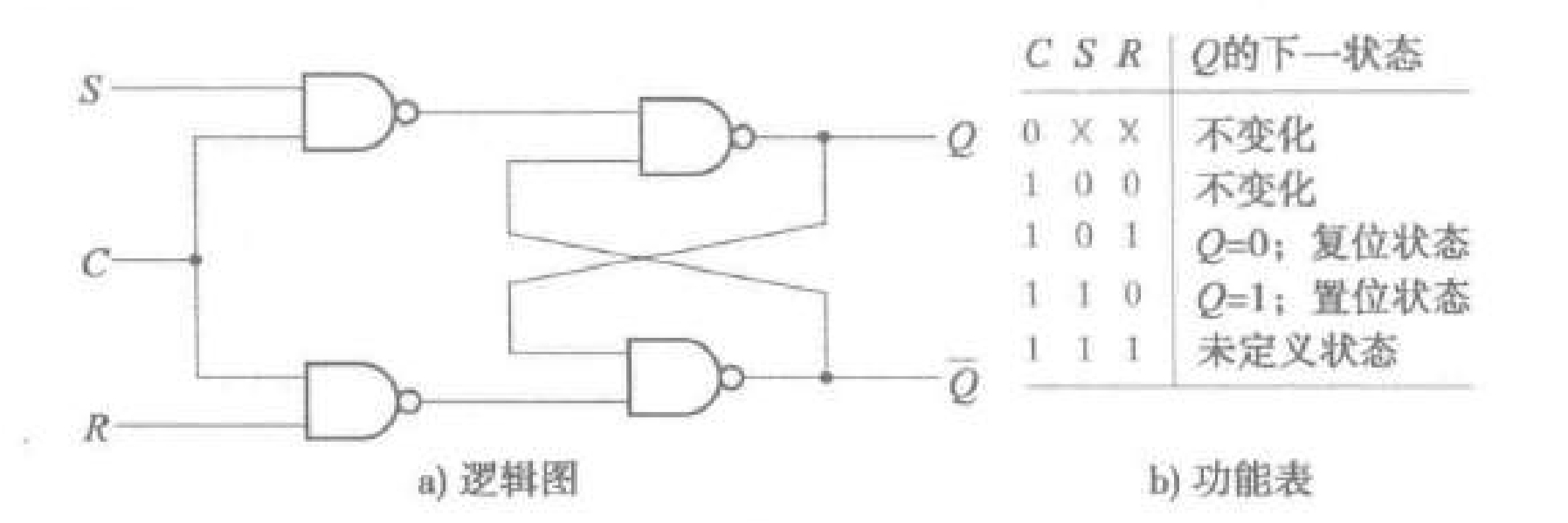

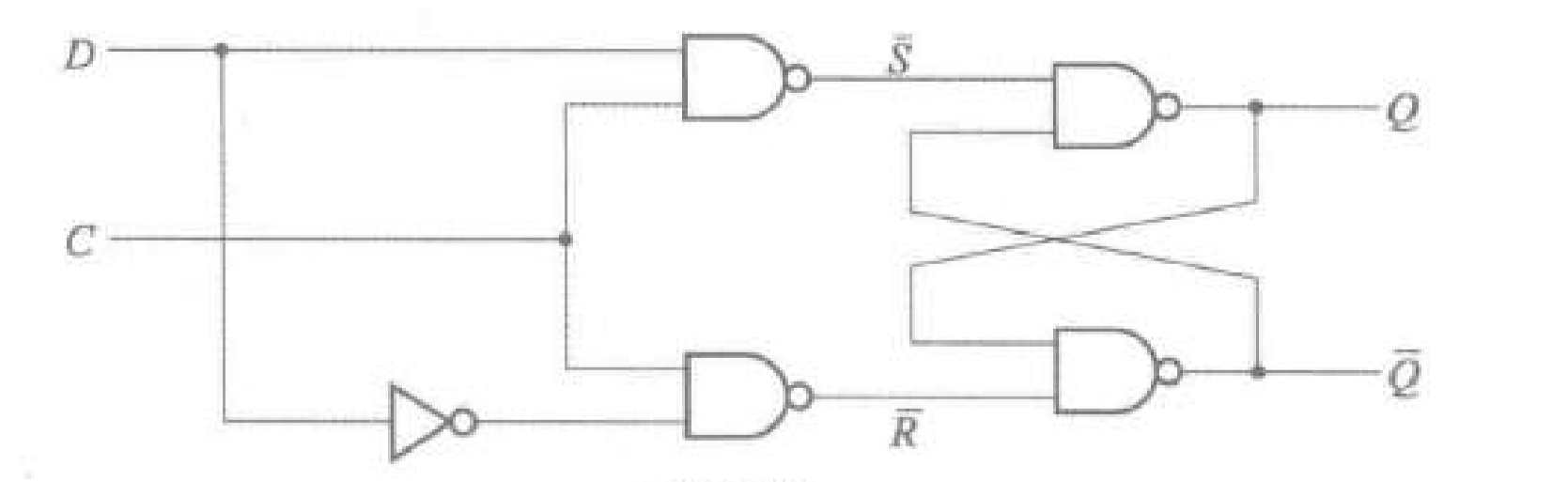

- 带控制输入 锁存器

- 锁存器

- 将 锁存器的 输入统一用 控制,得到 锁存器。

- 。

- 锁存器

- 性质

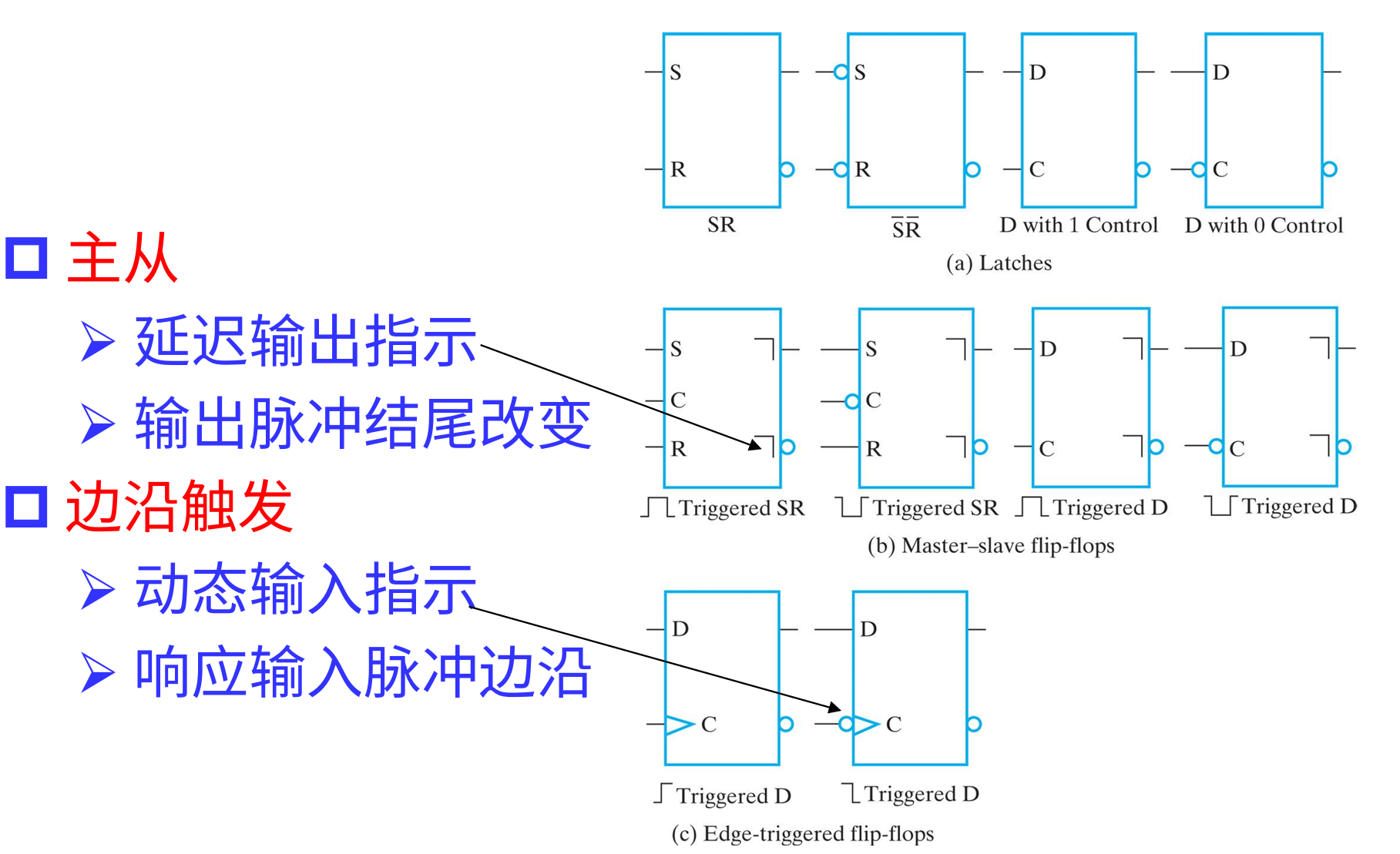

- 触发器

- 性质

- 触发器在一个时钟周期内状态只改变一次,输出不立刻改变。

- 脉冲触发器在时钟信号为特定值时可以改变状态,边沿触发器在时钟信号变化时改变状态。

- 分类

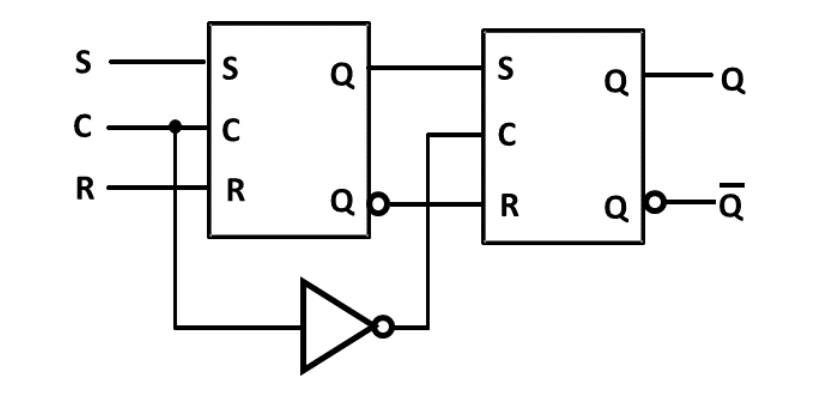

- 主从 触发器

- 主从 触发器是脉冲触发器。

- 主从 触发器由两个 锁存器组成,连接相反的时钟信号。

- 输入侧的是主锁存器,输出侧的是从锁存器。

- 主从 触发器的状态是从锁存器的状态。

- 上图为正脉冲主从 触发器

- 时接受输入,处于有效状态,但不改变输出。

- 时处于无效状态,由 变换到 时更新输出。

- 负脉冲版本只要接入取反时钟信号。

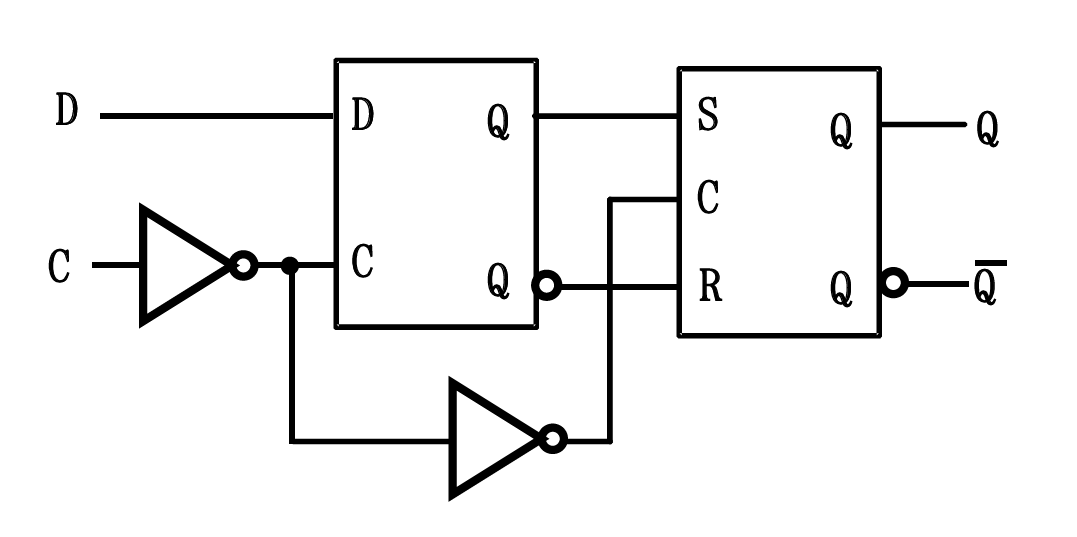

- 触发器

- 触发器是边沿触发器。

- 触发器由输入侧 锁存器和输出侧 锁存器组成,连接相反的时钟信号。

- 上图为正边沿 触发器,负边沿版本只要去掉时钟信号取反。

- 正边沿 触发器是标准触发器。

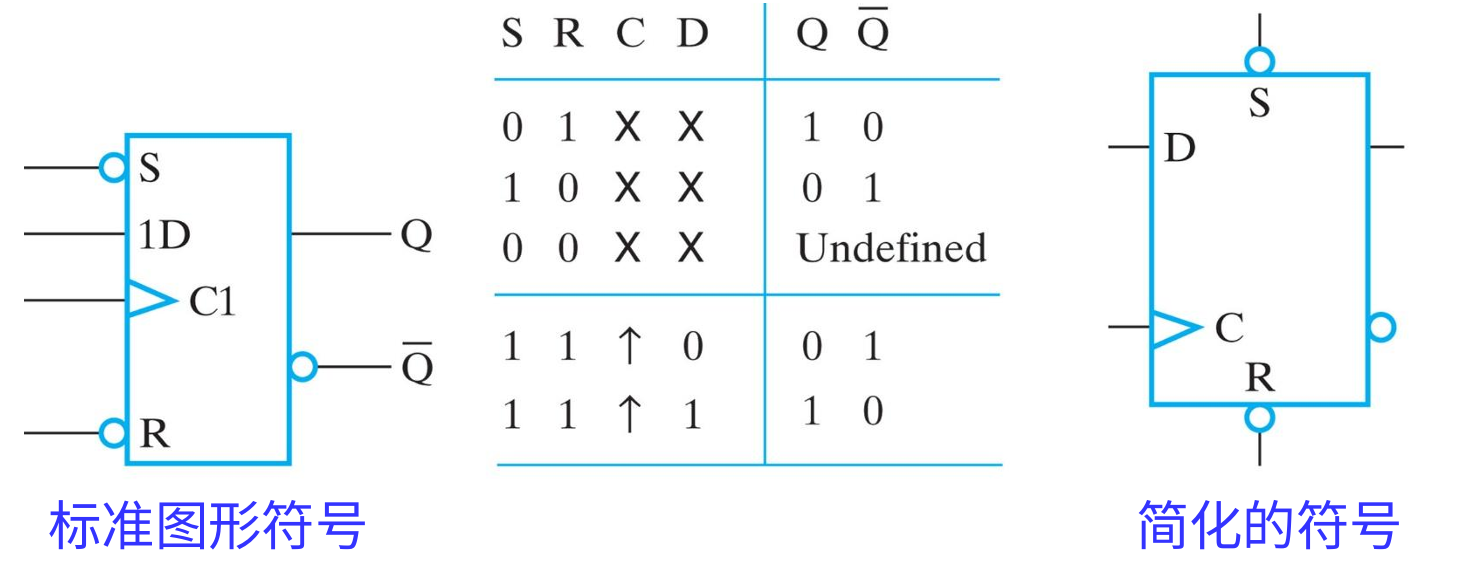

- 主从 触发器

- 直接输入

- 触发器有时需要进行初始化,此过程不依赖于时钟,需要使用直接输入。

- 在时钟信号和正常端口的字母前后标数字,表示信号与时钟的依赖关系。

- 直接输入为异步信号,不标数字。

- 标准符号

- 性质