时序逻辑电路分析

- 方程

- 时序逻辑电路包括状态,则有下一状态函数和输出函数。

- 下一状态函数表示为 或 。

- 输出函数分为 Mealy 型 和 Moore 型 。

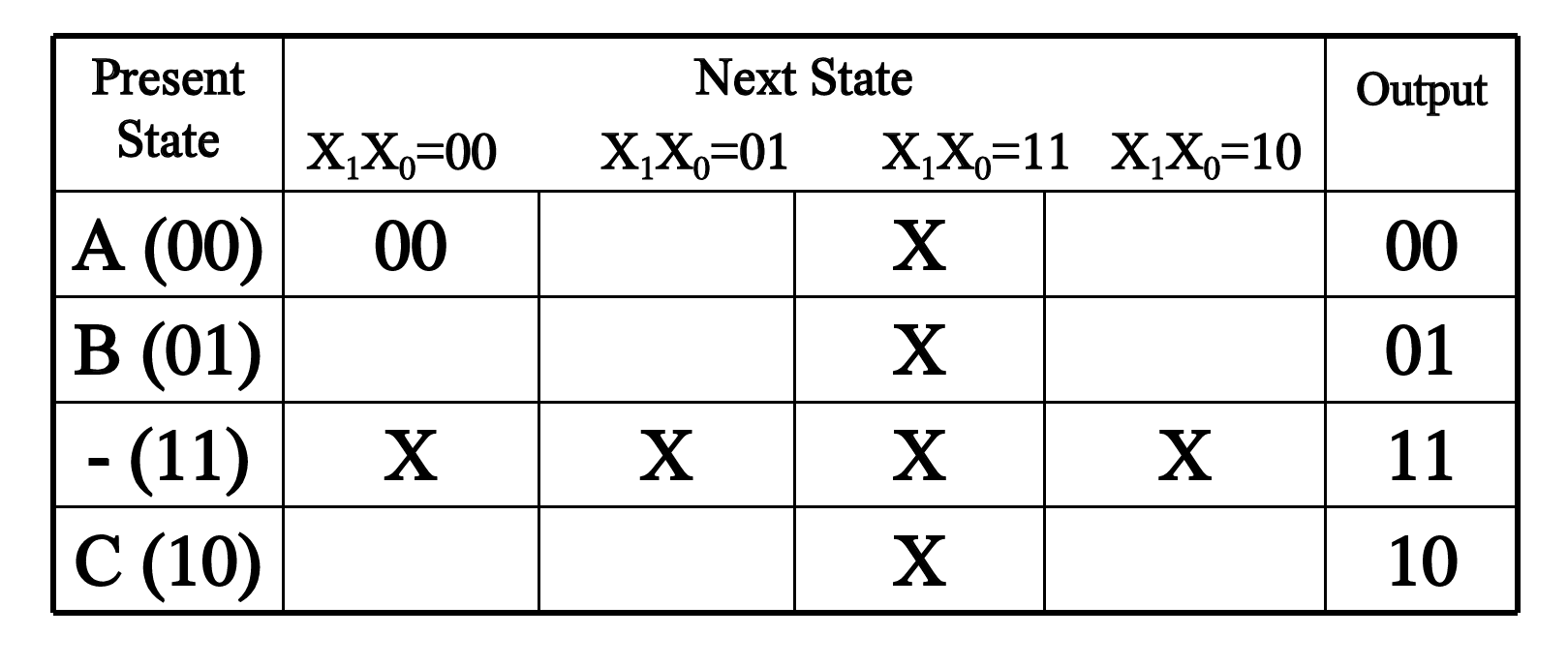

- 状态表

- 每一行对应每一个状态,列分为下一状态部分和输出部分,其中每一列对应一个输入,若为 Moore 型,输出部分只有一列。

- 将状态和输入组合按照格雷码排列,则可以直接得到卡诺图。

- 其中的无效状态用叉表示。

- 状态图

- 定义

- 状态图中每个结点是状态,有向边代表对应输入的状态转移。

- Mealy 型电路的输出在边上,Moore 型电路的输出在结点上,两种方式可以混合。

- 等价状态

- 如果某两个状态对每个输入都有相同的输出且转移到相同的状态,则两个状态等价。

- 等价状态可以合并为同一个状态。

- Mealy 型和 Moore 型转换

- Moore 型的输出比 Mealy 型的慢一个状态。

- Mealy 型转换为 Moore 型分为:

- 如果结点的入边上的输出都相同,则将此输出直接移动到结点上。

- 如果不同,拆分为两个输出不同的结点,按照边的输出连接入边,出边与原结点出边相同。

- Moore 型转换为 Mealy 型只要把每条边的下一状态结点的输出移动到边上。

- 状态分配

- 计数赋值:为每个符号按照顺序分配二进制编码。

- 格雷码赋值:为每个符号按照顺序分配格雷码。

- 单热点赋值:若有 种状态,则编码有 位,第 个状态编码第 位为 ,其他为 。

- 验证

- 手工验证:枚举所有状态和输入组合,验证下一状态或输出是否正确。

- 模拟验证:找到能够遍历整个状态图的路径对应的输入序列,验证下一状态或对应输出是否正确。

- Testbench

- 定义

- 状态机图

- 定义

- 状态机图是状态图的改进。

- 状态机图用布尔函数表示转移或输出条件,函数取值为 对应的输入可以转移或输出。

- 状态机图中变量有默认值 ,写出变量时此变量输出 。

- 转移行为

- 条件转移:布尔函数表示转移条件。

- 无条件转移:转移条件为 。

- 输出行为

- Moore 输出:变量输出只与状态有关。

- 非转移条件依赖(TCI)输出:变量输出与状态和输入有关,不发生状态转移。

- 转移条件依赖(TCD)输出:在状态转移时输出。

- 转移和输出条件依赖(TCOD)输出:在状态转移时输出,变量输出与输入有关。

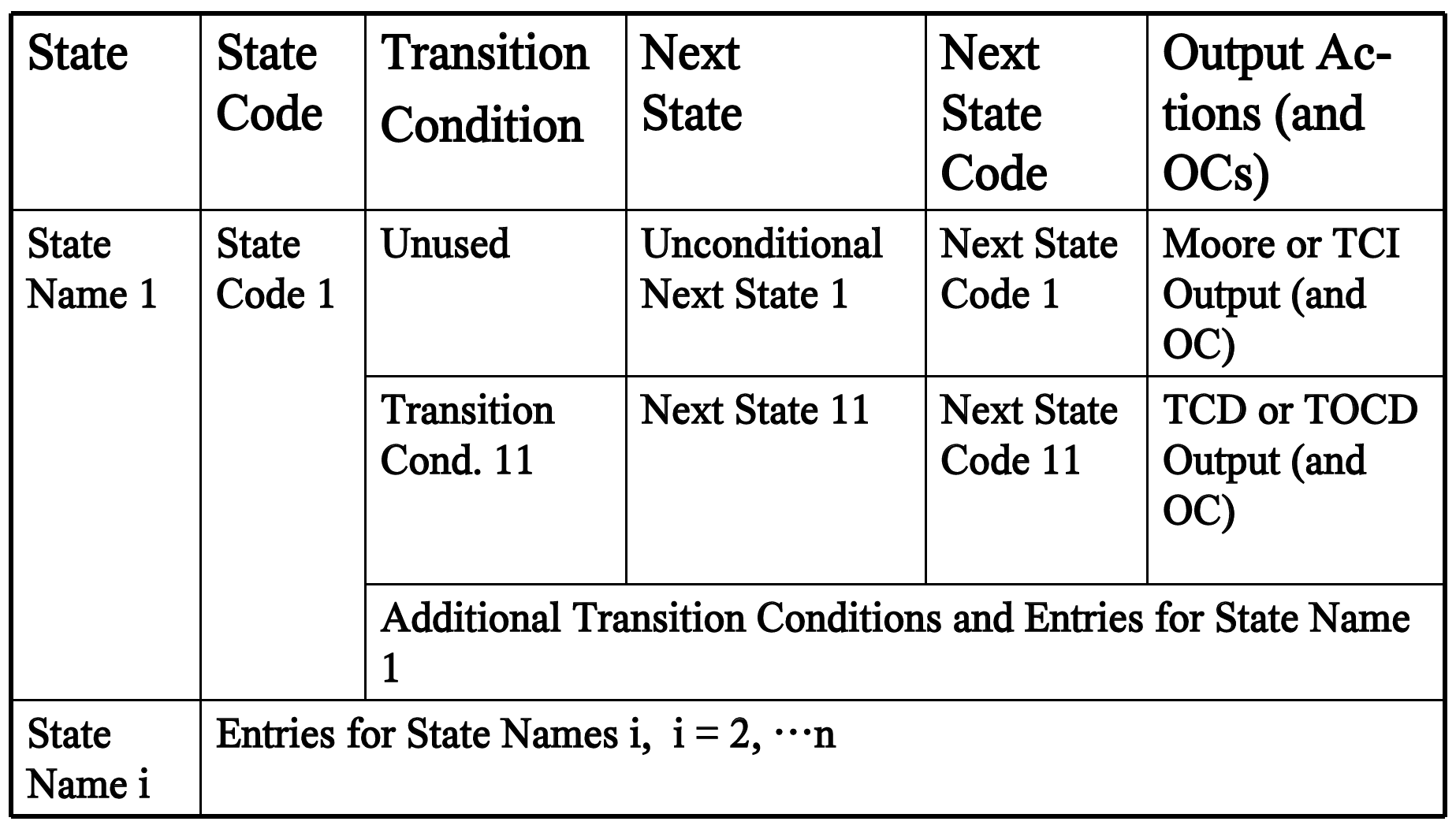

- 状态机表

- 对于依赖转移条件的输出,在最后加上

*。

- 定义