数字硬件实现

- CMOS 电路工艺

- 模型

- CMOS 晶体管包括三个极:源级、漏极、栅级,栅级控制源级是否与漏极导通。

- n 沟道晶体管:漏极为 时导通,记作 (栅级接入 )或 (栅级接入 )。

- p 沟道晶体管:漏极为 时导通,记作 (栅级接入 )或 (栅级接入 )。

- 开关电路

- 将 CMOS 电路的导通状态用接入栅级的变量表示,n 沟道与栅级相同,p 沟道相反。

- 电路串联则变量做与运算,电路并联则变量做或运算。

- n 沟道和电路 p 沟道电路有对偶性质,串并联的对偶按照与或的对偶。

- 反电路通过取原电路对偶再把所有晶体管改变类型(n 沟道变为 p 沟道或反过来,栅级接入的变量不变)。

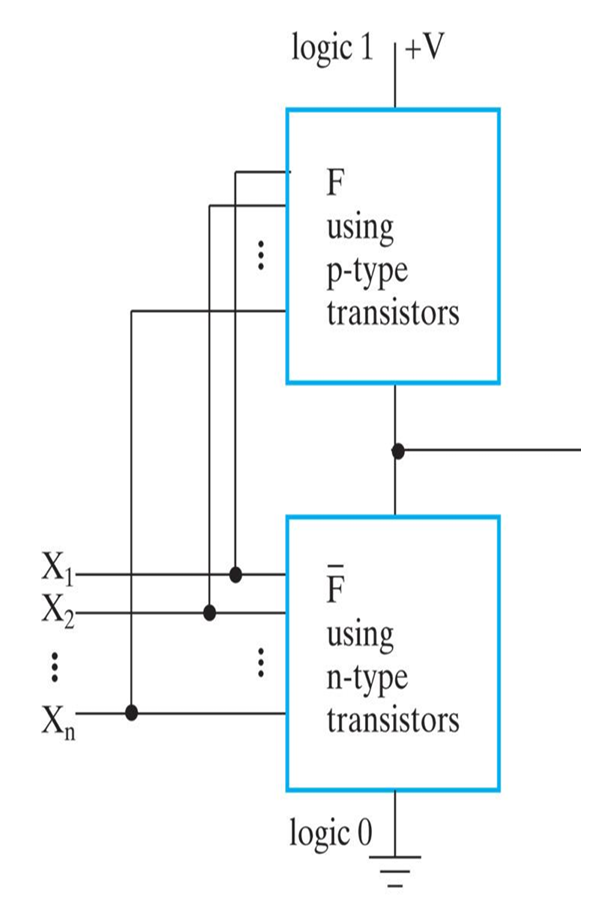

- CMOS 门结构

- n 沟道接 ,p 沟道接 。

- 对函数 设计门结构,先设计 的 n 沟道电路接 ,再用对偶性质取反得到 p 沟道电路接 。

- 模型

- 编程技术

- 分类

- 固化编程

- 熔丝

- 反熔丝

- 掩膜编程

- 可重复编程

- 编程点的存储单元:易失性

- 晶体管开关:不易失性

- 固化编程

- 可编程器件

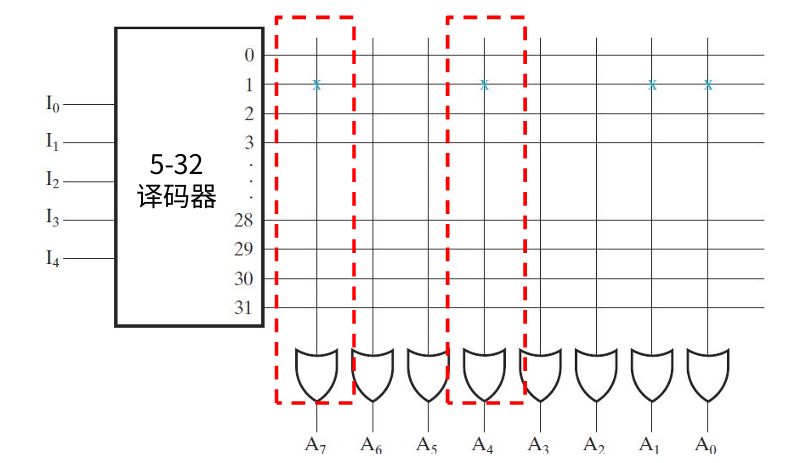

- 只读存储器(ROM)

- 固定与阵列,可编程或阵列。

- 由译码器提供最小项。

- 无需电路优化,但电路成本最高。

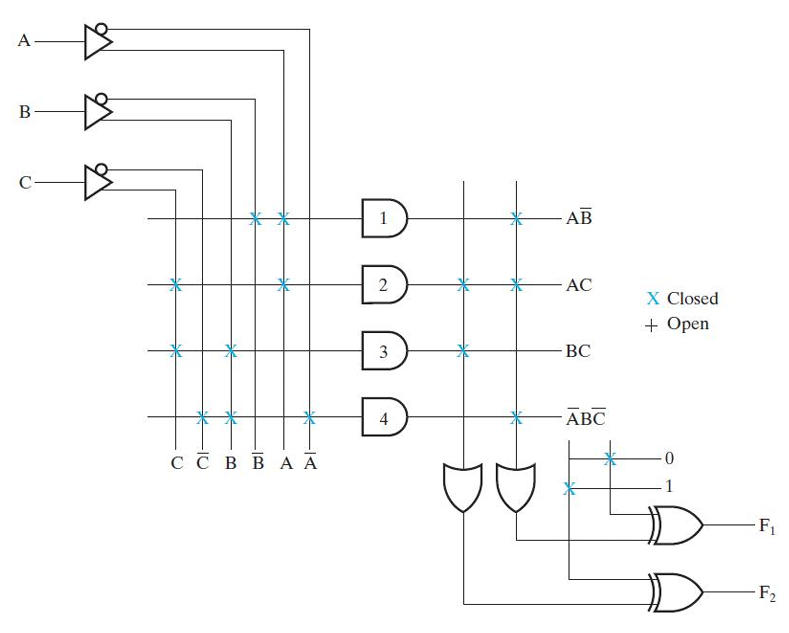

- 可编程阵列逻辑(PAL)

- 可编程与阵列,固定或阵列。

- 单输出两级优化,共享积之和。

- 有多级电路实现更复杂逻辑。

- 输入 输出 PAL 有 个缓冲非门、 个与门、 个或门。

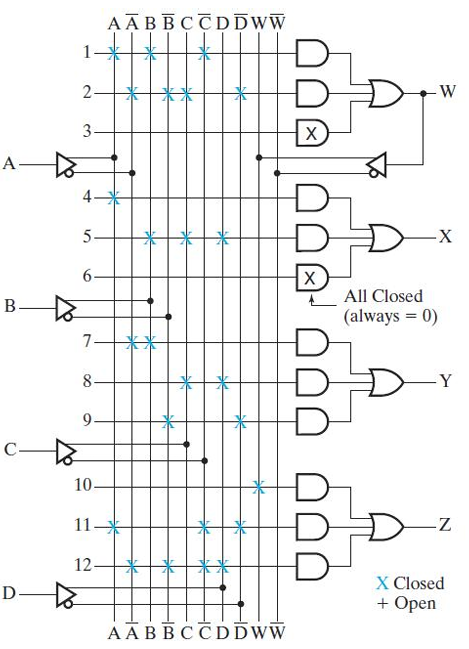

- 可编程逻辑阵列(PLA)

- 可编程与阵列、或阵列。

- 多输出两级优化,每个函数用最少乘积项,函数间共享乘积项。

- 可反相输出。

- 输入 输出 PAL 有 个缓冲非门、 个与门、 个或门、 个异或门。

- 只读存储器(ROM)

- 分类